探秘:英特尔22nm tri-gate晶体管技术

继四年前首度启用HKMG工艺制作商用处理器之后,全球最大的半导体厂商Intel又一次站在了业界前列,这一次他们用实际行动宣告与传统的平面型晶体管技术彻底告别。如先前外界所预料的那样,本周三Intel举办了一次新闻发布会,会上Intel高管Mark Bohr宣布Intel在22nm制程处理器中全面启用tri-gate晶体管技术,他并表示tri-gate晶体管技术的启用可以极大地减小晶体管的工作电压(51CTO推荐阅读:首个3D晶体管 英特尔技术实现重大突破)。

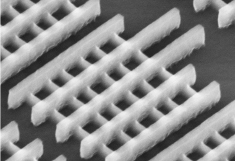

Intel 22nm制程tri-gate晶体管实物

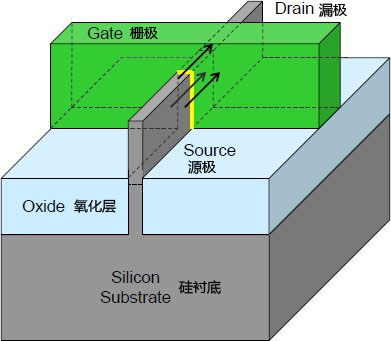

Inteltri-gate晶体管结构图

Bohr称:“转向立体型晶体管设计的最大好处是管子的工作电压和漏电流可以较大幅度地减小。”另外,他还表示制造tri-gate晶体管所用的晶圆成本仅比传统平面型晶体管高2-3%左右。

PS:Intel口中的tri-gate其实与人们通常所说的Finfet本质相同,有关tri-gate技术与Finfet技术读者可参考本站的这篇简介文章。

Bohr,Intel高级副总裁 Bill Holt以及架构总经理Dadi Perlmutter三人共同展示了在实际运行中的服务器,台式机以及笔记本,这些设备上均装用了22nm制程的Ivy Bridge处理器,这款处理器产品将于明年早些时候正式上市。

#p#

全面启用tri-gate技术

与之前人们猜想的情况有所不同,Bohr在发布会上称Intel的22nm制程处理器中所有的晶体管均采用tri-gate制作,而此前人们猜想的情况是仅有SRAM部分采用了tri-gate,而逻辑电路部分仍采用传统的平面型晶体管结构。另外,Bohr还透露在Intel的22nm制程处理器中,有些部分的晶体管电路采用了6鳍设计(在Finfet中,Fin即鳍的部分相当于平面型晶体管中的沟道),而有些部分的晶体管电路则仅采用2鳍设计,举例而言,SRAM晶体管部分的晶体管结构便于逻辑晶体管的结构有所不同,在tri-gate的基础上做出了一些改动。

另外Bohr还表示,Intel在14nm节点仍将继续使用tri-gate晶体管技术,不过届时Intel可能会进一步增加tri-gate晶体管中鳍部分的高度,以增强管子的性能,另外芯片内含的晶体管密度也将比22nm节点大幅增加。

Bohr透露,Intel早已决定要在22nm节点放弃50年来人们一直在使用的平面型晶体管技术。Intel的tri-gate晶体管技术其实属于Finfet的一种变种,采用这种结构的晶体管其沟道垂直与衬底,沟道的三个面则被三个栅极围绕,这种结构可以增强栅极对沟道的控制作用,从而进一步提升管子的电流驱动能力和省电性能。

#p#

tri-gate晶体管的性能提升

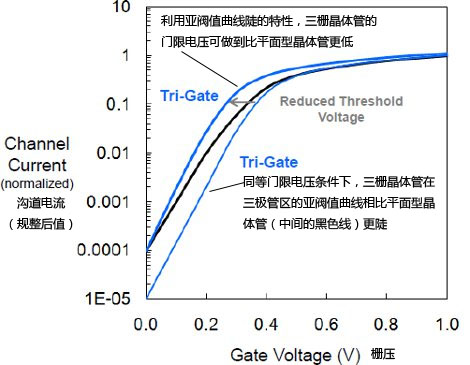

Intel公布的22nmtri-gate晶体管沟道电流值

与Intel目前最好的32nm制程工艺比较,22nm制程立体型晶体管工作电压Vdd仅0.7v,平面型晶体管则很难达到这样的工作电压水品,同时管子的性能则比前者提升37%。同时,管子的延迟时间可以在输入电压比32nm制程低0.2v(即0.8V)的条件下保持在原有的水平。

他说:“22nm制程tri-gate技术的晶体管性能基本与32nm制程一致,但输入电压仅0.8V,比后者的1.0V更低,这样工作状态下管子的功耗可减小50%以上。”

#p#

tri-gate与平面型体硅及FDSOI技术的优劣对比:

会上Bohr还简要介绍了一些晶体管器件物理学方面的知识。据他介绍,由于平面型体硅晶体管的衬底部分存在微小电压,因此很难优化管子的亚阀值(sub-threshold,台湾人的说法是次临界,即晶体管的栅电压低于门限电压的情况)性能。而FDSOI器件虽然可以解决这个问题,但是制造FDSOI器件的超薄体SOI晶圆成本太高。在谈到由意法半导体等公司主推的超薄体SOI技术时,Bohr则称由于这种SOI晶圆的埋入氧化层与其顶部超薄硅层之间的距离非常小,因此对超薄体SOI晶圆的制造技术提出了非常高的要求。

“虽然已经有人制造出这种超薄体SOI晶圆,但是其价格太高,而且制造难度也很大。”他并表示Intel认为这种超薄体SOI晶圆的最终成本可能会(比常规SOI)高出10%。与此类似,FDSOI阵营的成员也承认超薄体SOI的成本相对较高,但是他们强调FDSOI可以降低所需的隔离结构等的数量,因此FDSOI可以间接降低掩模板制作方面的成本,这里节省的成本则可以与晶圆增加的成本大致相抵。

Perlmutter则在会上表示,Intel的22nm产品输入电压将更低,而且同时与32nm平面型晶体管相比,22nmtri-gate晶体管功耗更低,晶体管面积则可减小一半左右。目前,Intel Atom系列SOC产品的使用率还不是很高,其主要的原因之一就是其对手基于ARM架构的SOC功耗相对更低。Perlmutter表示Intel将尽快将22nmtri-gate制程引入到Atom系列产品上,并称转换的步调要比从过去从45nm转换到32nm的步调更快。

#p#

tri-gate技术在实际产品上将如何部署

据Intel透露,最先使用22nmtri-gate技术制作的处理器产品将是双核设计的Ivy Bridge处理器,不过Atom内核的产品也非常需要22nmtri-gate技术。“Atom方面的需求是非常迫切的。22nmtri-gate技术不仅省电,而且还可以给Atom系列产品带来更高的性能。”

VLSI Research市调公司的CEO Dan Hutcheson认为此次Intel转向tri-gate设计具有“历史性的意义”,是50多年前Bob Noyce, Jack Kilby等人发明首款平面型晶体管之后的又一次重要变革。Gartner公司的分析师Dean Freeman则干脆表示:“Intel这次干的太漂亮了!”

尽早转向Finfet技术“让Intel找到了移动设备市场的一个极好突破点,因为这种技术的省电性能极好,其性能表现则可以将ARM一族打得溃不成军。”

其它厂商在Finfet方面的动向:

除了Intel之外,ARM架构SOC的代工大厂台积电公司不久前也宣布会转向Finfet技术,不过按他们此前宣布的计划,要到14nm节点才会完成转型。至于IBM及其合作伙伴,Freeman认为他们同样不太可能在14nm节点之前转向Finfet技术。

#p#

制作tri-gate晶体管的技术难点

Gartner的分析报告称要实现Finfet技术,需要克服许多制造技术方面的难关。比如要制造出Finfet晶体管,要求光刻机的图像对准性能较好。“过去人们认为只有采用EUV光刻机才有可能制造出Finfet晶体管,不过由于ASML或者尼康生产的193nm液浸式光刻机具有极高的套准精度(overlay),因此也有可能采用这种光刻机制造出Finfet晶体管。”

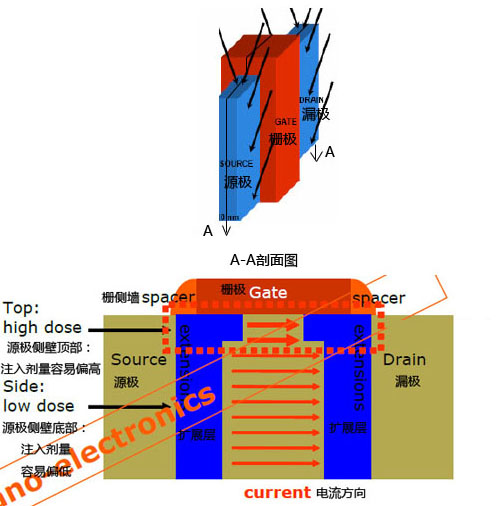

Finfet侧墙掺杂密度控制示意图

另外,尽管采用PIII(Plasma-immersion ion implantation)离子注入工艺可以实现,但如何保证Fin两侧漏源极侧墙部位从上到下杂质掺杂(目的是减小漏源极的电阻)密度的均匀性则是另外一个Finfet制造的难题。

此外,制造Finfet结构时蚀刻Fin时如何保证Fin侧壁的粗糙度控制在一定的水平之内则是另一个难题。

【编辑推荐】

- 首个3D晶体管 英特尔技术实现重大突破

- Intel资深专家:32纳米之后的摩尔定律

- 十载寒窗 英特尔至强处理器历代记

上一篇:惠普CP3525dn彩色激打促销

下一篇:硬盘软故障修护手册